Reverse Engineering Custom ASICs by Exploiting Potential Supply-Chain Leaks

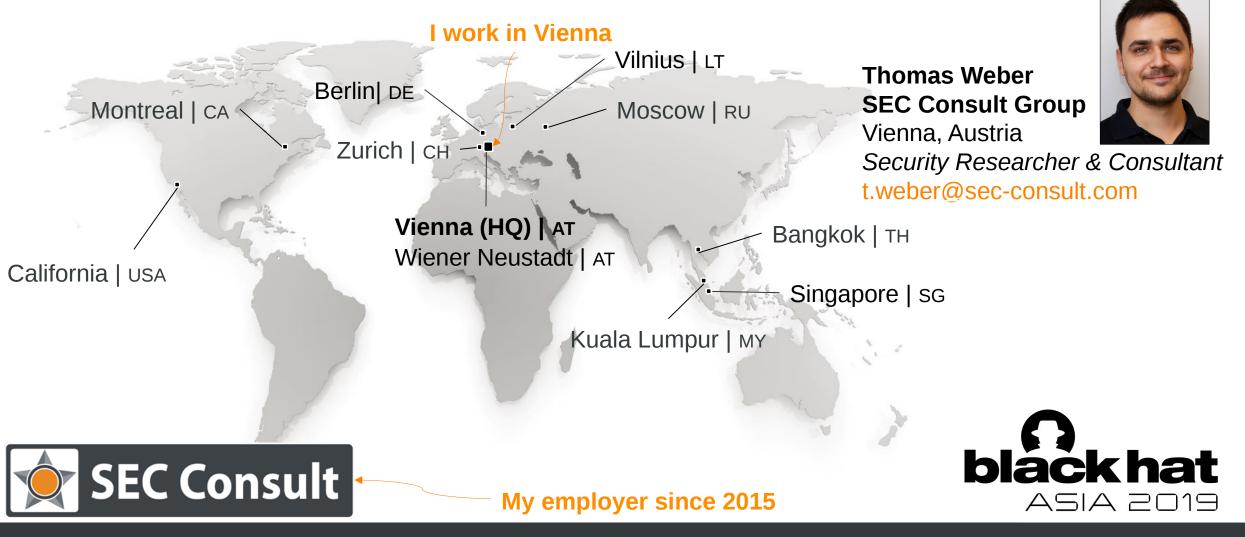

### \$ whoami

## Outline

At a glance:

- Introduction & motivation important notes

- Dangers of supply-chains

- Reverse engineering methods

- Deductive reasoning probing methods

- Deeper insights

- Live debugging & demo

- Fun fact

- Conclusion

## Introduction

#### What is an ASIC?

- → Application Specific Integrated Circuit

- → Can also be a System on Chip solution with customized peripherals (theoretically everything)

#### Who cares?

- → Vendors, security researchers, blackhat hackers...

Where is it used?

- → In every (embedded) computer system. There are more precise names for the specific applications like SoC, ASIP, NoC and so on.

## Introduction

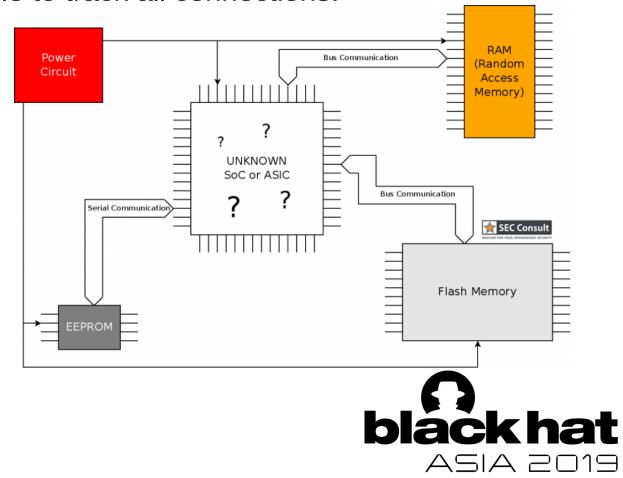

It gets hard when there are **complete custom** chips without public documentation.

This means:

- → Architecture is **unknown**

- → Pinout is unknown

- → I/O memory map is **unknown**

- → Additional constraints are **unknown**

- $\rightarrow$  Sometimes, even the vendor is **unknown**

### **Motivation**

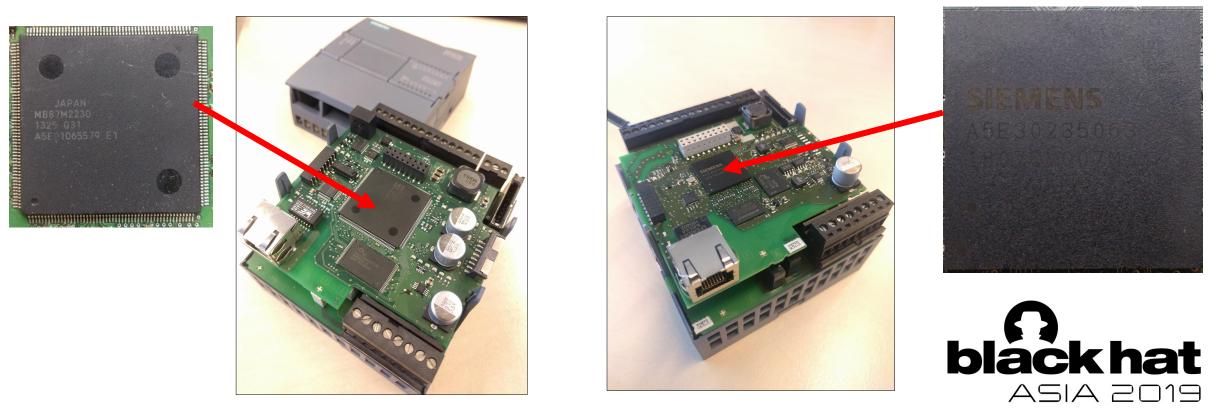

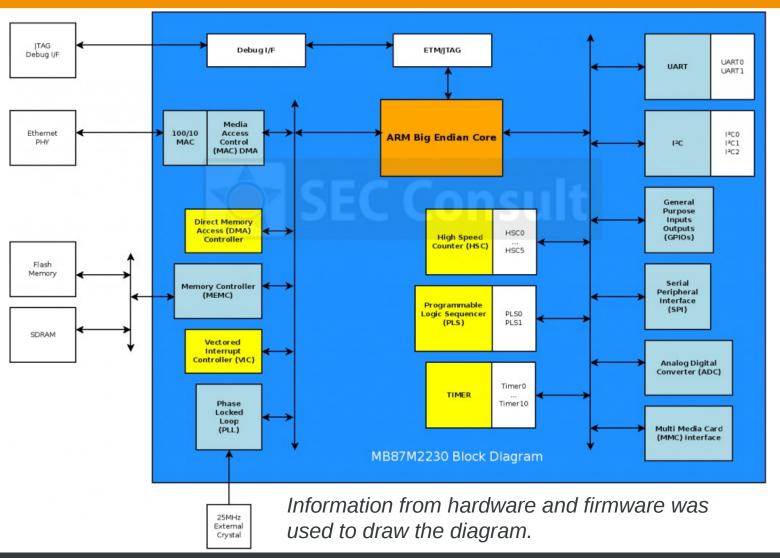

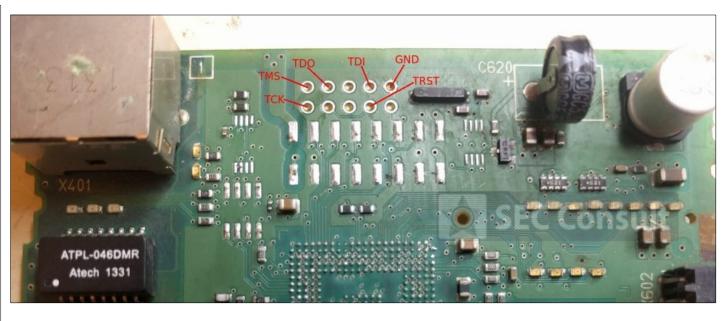

A textbook example for custom ASICs can be found inside of industrial products like the PLC series S7-1200. There are even different hardware versions of this PLC series, and two different main chips. **Can we identify the JTAG port?**

### **Motivation**

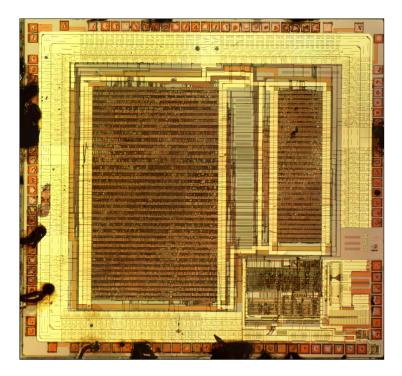

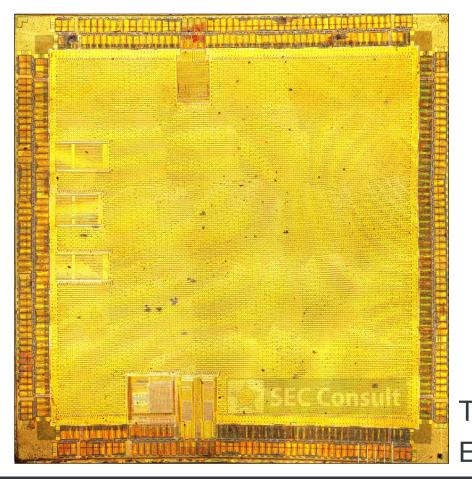

**Expensive option:** Decapping, FIB or SEM and delayering, recover the hardware. *From silicon die... ... to hardware description.*

Source: https://www.capovani.com

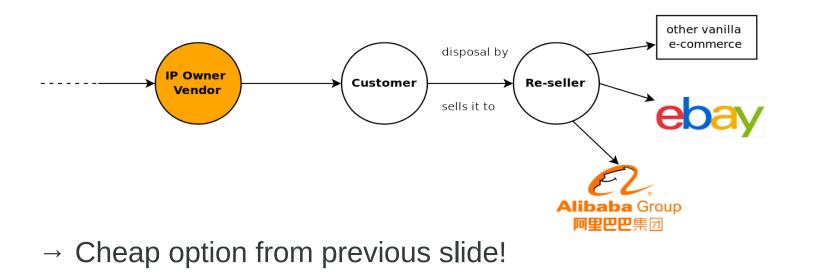

## **Motivation**

**Cheap option:** Search for similar hardware with the same chip on the internet. Good sources are: strange online shops, eBay, AliExpress and Taobao ( 淘宝网 ) Multiple PCBs with the same chip are even better to reverse engineer each pin functionality. The possibility to identify debug ports by having multiple different PCBs with the same chip is higher.

#### Bad:

Not all secrets of the hardware can be revealed in that way.

#### Good:

No need for super expensive equipment!

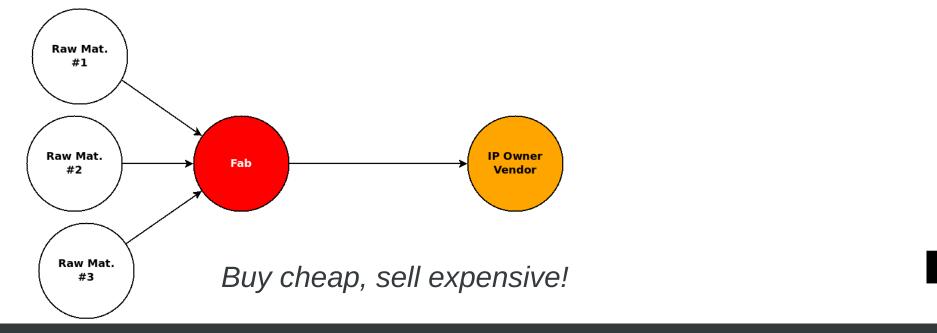

Supply-chains often involve exposure of IP(Intellectual Property) to 3<sup>rd</sup> parties.

#### **Example: Super fancy chairs**

I want to produce cheap fancy chairs in another part of the world to save costs. For that, I have to send the blueprints to the factory, which delivers the chairs  $\rightarrow$  The intellectual property is exposed. For more complex chairs, I also need prototypes.

Title: SEC Consult – Reverse Engineering Custom ASICs by Exploiting Potential Supply-Chain Leaks | Responsible: T. Weber | Version / Date: V1.0/2019-03 | Confidentiality Class: public © 2019 SEC Consult | All rights reserved

באום בח

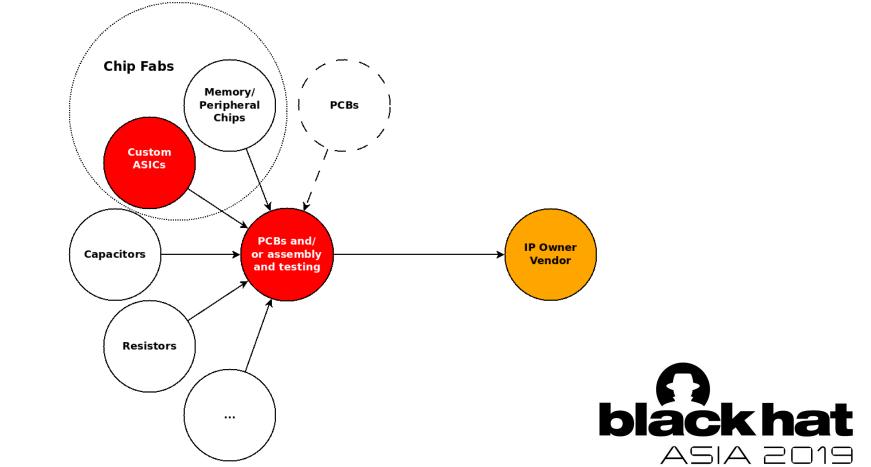

Producing electronics is similar to the latter example but more complicated.

Example: PLC Memory Chips Custom Chips Capacitors Capacitors Resistors PCB and testing and so on...

Producing electronics is similar to the latter example but more complicated.

**Example: PLC** Memory Chips **Chip Fabs** Memory/ Custom Chips → IP Peripheral PCBs Chips Capacitors Custom ASICs Resistors PCB and testing  $\rightarrow$  IP PCBs and/ **IP Owner** Capacitors or assembly Vendor and so on... and testing Resistors **bláčk hat** ... A51A 2019

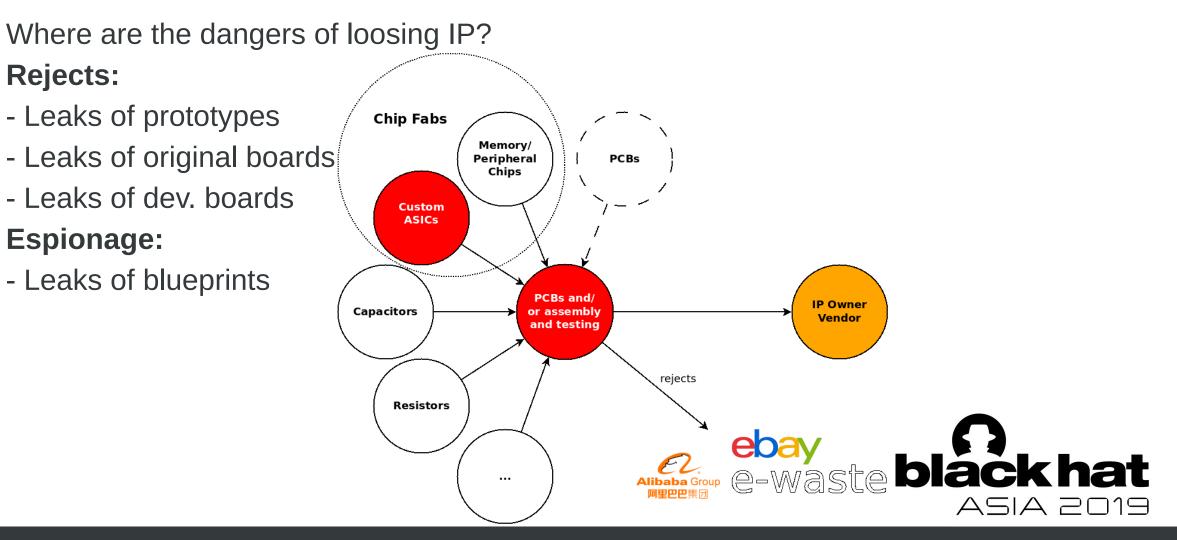

#### Where are the dangers of losing IP?

#### **Aftermarket issues:**

A product, which is hard to unearth (very expensive or just available when you have a contract with the vendor) is available in big cheap batches from a re-seller. This enables you to do reverse engineering even with a small budget.

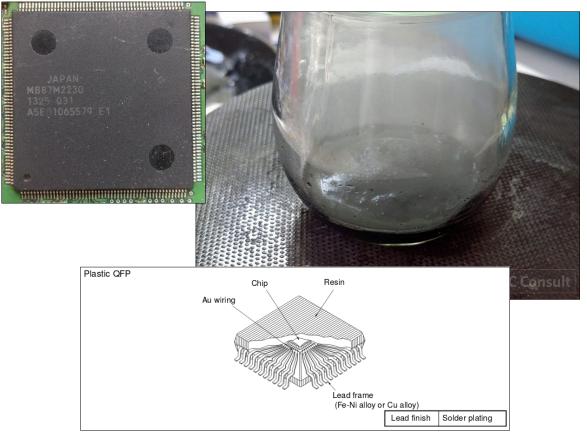

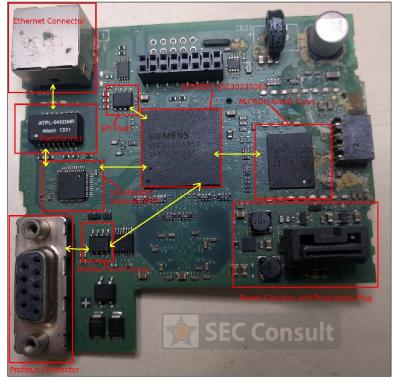

Searching for the label of the ASIC used in the older S7 1200v1 on Google gave some results, one of them was Taobao:

MB87M2230

Taobao just sells stuff inside China. Colleagues and friends from Singapore and China came to the rescue!

Two batches were ordered one after the other.

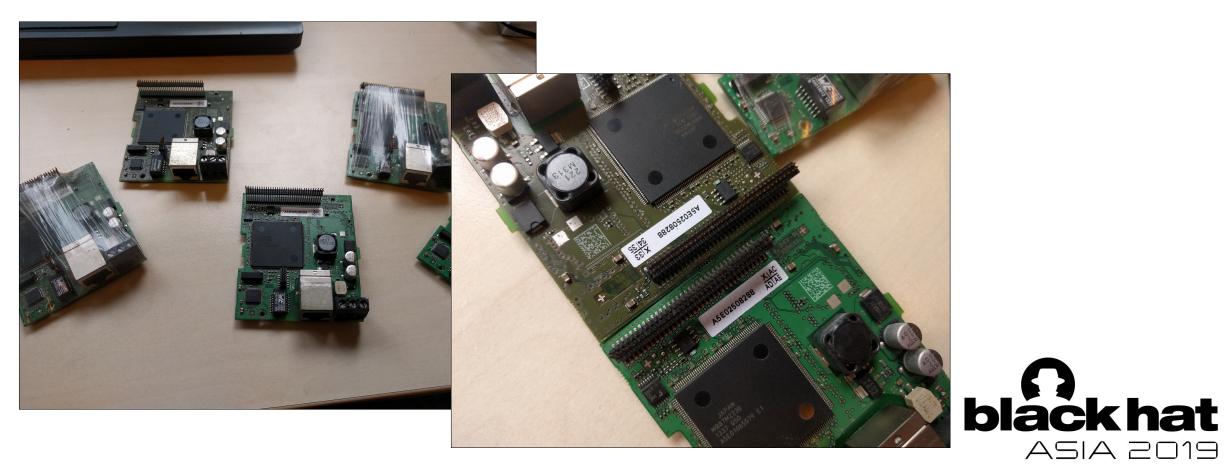

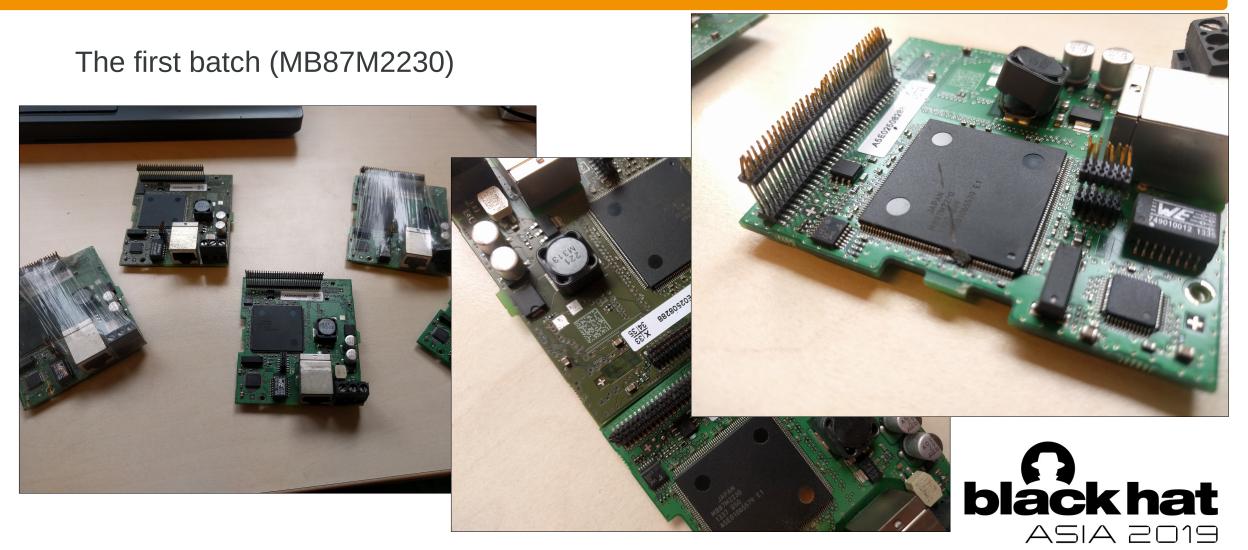

#### The first batch (MB87M2230)

#### The first batch (MB87M2230)

#### The first batch (MB87M2230)

Searching for the label of the ASIC used in the newer S7 1200v4 on Google gave some results, one of them was Taobao, again from the same seller:

The second batch (A5E30235063)

#### The second batch (A5E30235063)

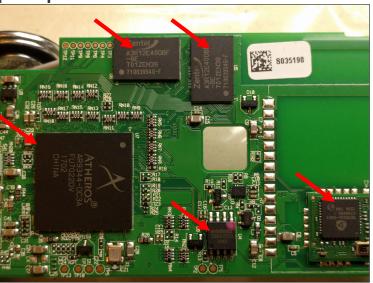

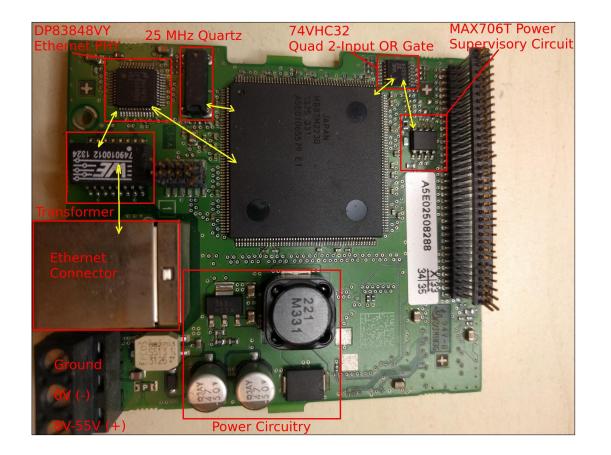

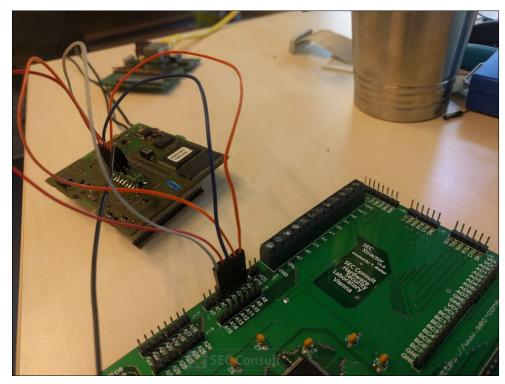

## Reverse engineering methods – First batch of PCBs

Collecting datasheets by looking at the PCB:

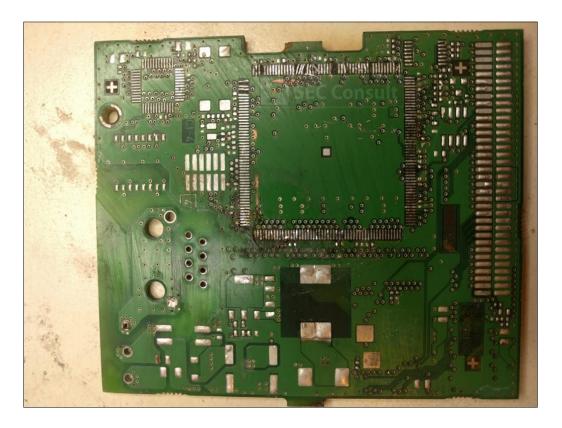

Remove all parts from one PCB to be able to track all connections.

Determining the obvious Vdd pins.

#### **Reverse engineering methods – Deductive reasoning**

Actively probing for debug interfaces, in this case for JTAG. Some pins were excluded from this test because of the prior step.

These pins are often pulled to Vdd by using a pull-up resistor! They may be close to SPI or UART!

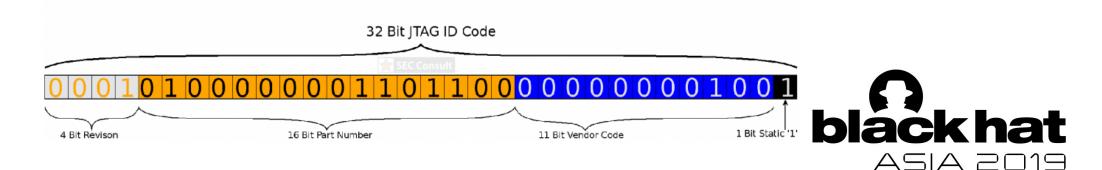

After finding such a JTAG port, the ID-code can be fetched and interpreted:

| [root@003-0089-0053 ~]# openocd -f /home/cfg                                                           |

|--------------------------------------------------------------------------------------------------------|

| Open On-Chip Debugger 0.10.0-dev-00247-g73b676c (2016-05-02-15:42)                                     |

| Licensed under GNU GPL v2                                                                              |

| For bug reports, read                                                                                  |

| http://openocd.org/doc/doxygen/bugs.html                                                               |

| adapter speed: 500 kHz                                                                                 |

| jtag                                                                                                   |

| Info : clock speed 500 kHz                                                                             |

| Warn : There are no enabled taps. AUTO PROBING MIGHT NOT WORK!!                                        |

| Info : JTAG tap: auto0.tap tap/device found: 0x1406c009 (mfg: 0x004 (Fujitsu), part: 0x406c, ver: 0x1) |

| Warn : AUTO auto0.tap - use "jtag newtap auto0 tap -irlen 5 -expected-id 0x1406c009"                   |

| Warn : gdb services need one or more targets defined                                                   |

| ADVISOR FOR INFORMATION SECONT                                                                         |

Refer to JEDEC "JEP106AV"!

Besides JTAG, another challenging task is the detection of reset pins (SRST not TRST).

Common design patterns can help here, e.g.:

- The reset pin might be **bound to Vdd by** the **same** pull-up **resistor value** like all other ICs.

- The reset pin might be switched from Vdd to GND by using a transistor.

- $\rightarrow$  These two cases are very likely!

Quick test: Short circuit the pin to GND (be sure to not kill the power IC) BINGO!  $\rightarrow$  When the CPU jumps to its reset vector!

#### **Reverse engineering methods – Deductive reasoning**

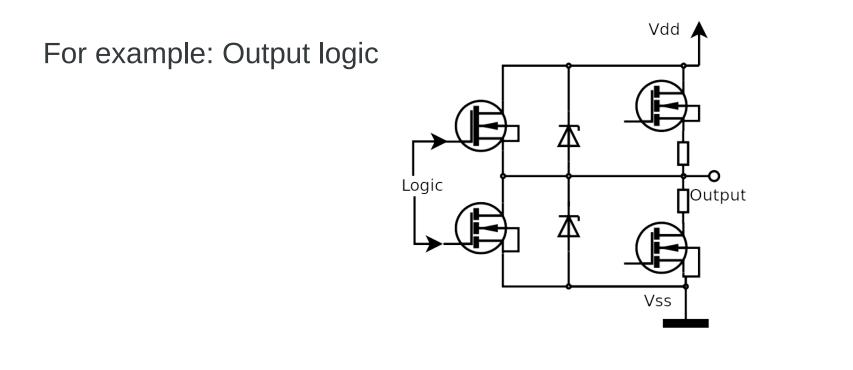

Whether a pin is an input, output or inout pin, can be determined by measuring the resistance of a pin. This is different from chip to chip and can be used as last step to identify the possible purpose of a pin.

## **Deeper insights**

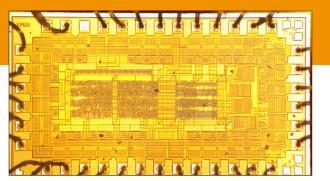

#### Delicious cooking in sulfuric acid!

## **Deeper insights**

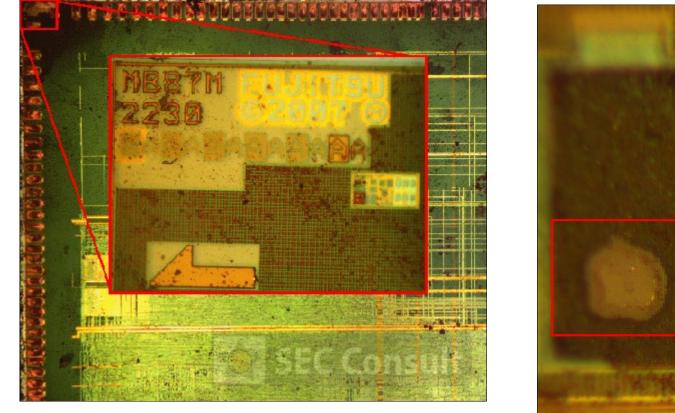

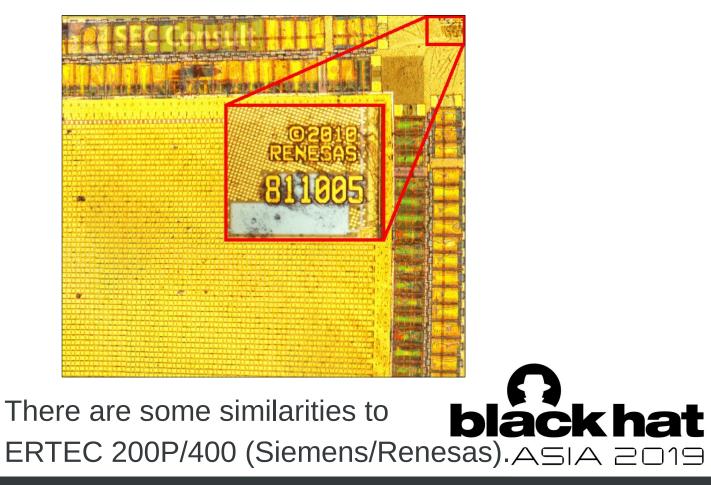

The labels on the bare die sometimes reveal important information.

For this chip, it was good to verify the JTAG output – it was designed by Fujitsu.

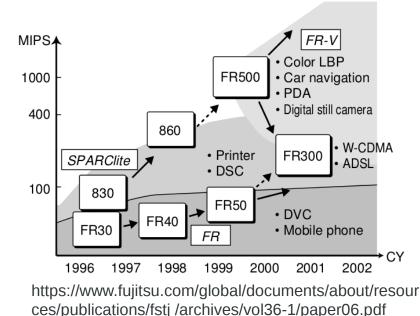

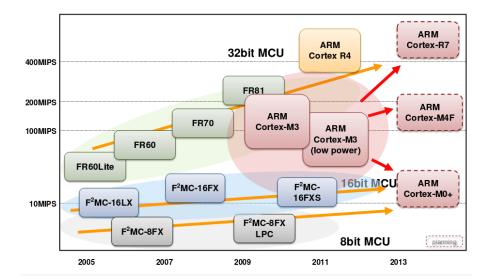

# Deeper insights – Digging through the literature

#### So many possibilities!

http://docplayer.net/4207609-Right-sized-solutions-forembedded-applications.html

Other MB8xMxxxx chips have ARC Tangent processors, **black hat** or Fujitsu RISC (FR). It can also be F<sup>2</sup>MC....

## **Deeper insights**

Removing the flash memory and reading out its content always helps.

## **Deeper insights**

By combining the information of the used CPU core, the year and the available IP cores from Fujitsu at that time we can be pretty sure that ARM926/ARM946 is used.

The second batch of PCBs can be analyzed in the same way as the first one.

The different architectures of SPI flash + NAND flash were one of the first observations.

The bootloader, which is located at the SPI flash memory was dumped and loaded into IDA Pro:

| Functions window |         |          | □ @ ×      |                                      | IDA View-A         |          | Pseudocode-A |          | 5       | Strings win | wobr   | 3        | He       | x View-1 | 8       | A       | Structures  |        |

|------------------|---------|----------|------------|--------------------------------------|--------------------|----------|--------------|----------|---------|-------------|--------|----------|----------|----------|---------|---------|-------------|--------|

| unction name     | Segment | Start    | Length ^   |                                      |                    | (v19, 3) | ;            |          |         |             |        |          |          |          |         |         |             |        |

| sub_3508         | ROM     | 000035C8 | 00000240   | 149<br>150                           |                    |          |              |          |         |             |        |          |          |          |         |         |             |        |

| sub_CA3C         | ROM     | 0000CA3C | 00000240   | 150                                  |                    |          |              |          |         |             |        |          |          |          |         |         |             |        |

| sub_6088         | ROM     | 00006088 | 00000244   | • 152                                |                    | ( 66     |              |          |         |             |        |          |          |          |         |         |             |        |

| sub_29F0         | ROM     | 000029F0 | 0000024C   | 153                                  |                    |          |              |          |         |             |        |          |          |          |         |         |             |        |

| sub_708C         | ROM     | 0000709C | 00000258   | • 154                                |                    |          |              |          |         |             |        |          |          |          |         |         |             |        |

| sub_E740         | ROM     | 0000E740 | 00000258   | • 155                                |                    |          | * v2 + 2686  |          |         |             |        | 1000     |          | 100 M    |         |         | Sector Part |        |

| sub_2558         | ROM     | 00002558 | 0000025C   | • 156                                |                    | D8(*(un  | signedint    | 16 *)(20 | a * v2  | + 0x100     | 30012) | , &v34,  | &v37, &  | W36, &v  | 38, 268 | 656540, | &v35, 0,    | &v39); |

| sub_FA78         | ROM     | 0000FA78 | 00000260   | <ul> <li>157</li> <li>158</li> </ul> |                    | - "cp -  | age read fai | Duffe -  |         | 1 00000     | +1/20  |          | 100300   | 1011.    |         |         |             |        |

| sub_SDA4         | ROM     | 00005DA4 | 00000270   | 158                                  |                    | , uk p   | age read fai | 03.84.4  | *** *   | C_DWOKD     | 1(20   | V2 4 6   | ×100306  | 10));    |         |         |             |        |

| sub_FCD8         | ROM     | 0000FCD8 | 00000294   | 0 168                                |                    | v35 )    |              |          |         |             |        |          |          |          |         |         |             |        |

| sub_88C          | ROM     | 0000089C | 00000284   | 161                                  |                    | 1        |              |          |         |             |        |          |          |          |         |         |             |        |

| sub 8824         | ROM     | 00006824 | 00000288   | • 162                                | v26 = 2;           |          |              |          |         |             |        |          |          |          |         |         |             |        |

| sub_11218        | ROM     | 00011218 | 000002C8   | • 163                                |                    |          | nc error 8x% | 4.4X 0x3 | EX Buck | X BOOK",    | *(_DW  | ORD *)(2 | 0 * v2   | + 0x100  | 30010), | v2, v3  | 4, v35);    |        |

| sub_532C         | ROM     | 0000532C | 000002DC   | • 164                                |                    |          |              |          |         |             |        |          |          |          |         |         |             |        |

| sub_1FE4         | ROM     | 00001FE4 | 0000031C   | 165                                  |                    |          |              |          |         |             |        |          |          |          |         |         |             |        |

| sub E998         | ROM     | 0000E998 | 00000344   | <ul> <li>166</li> <li>167</li> </ul> |                    |          | 0 * v2 + 0x1 | 8038014  | );      |             |        |          |          |          |         |         |             |        |

| sub_10DFC        | ROM     | 00010DFC | 00000350   | 168                                  |                    | 1 020    |              |          |         |             |        |          |          |          |         |         |             |        |

| sub_785C         | ROM     | 0000785C | 00000368   | • 169                                |                    | 2. "GR c | rc mismatch  | 8x64.4X  | exdix.  | exax exac   | x". *( | DWORD *  | )(20 *   | v2 + 0x  | 1003001 | e), v2, | V27, V28    | ):     |

| sub_F628         | ROM     | 0000F628 | 00000368   | • 178                                |                    |          |              |          |         |             |        |          |          |          |         |         |             |        |

| sub_10298        | ROM     | 00010298 | 0000046C   | 171                                  |                    |          |              |          |         |             |        |          |          |          |         |         |             |        |

| sub_BF7C         | ROM     | 00008F7C | 00000574   | • 172                                |                    |          | 0 * v2 + 0x1 | 803801C  | );      |             |        |          |          |          |         |         |             |        |

| sub_050          | ROM     | 00000050 | 0000061C   | • 173                                |                    | v29 )    |              |          |         |             |        |          |          |          |         |         |             |        |

| sub_1071C        | ROM     | 0001071C | 000006E0   | 174                                  |                    |          | ersion misma | tch and  | . AV 0  | AV DAY      | a Av   | */ 200   | DD #1/2  |          | 0-100   | 20010   | 10 10 E     | 1000   |

| sub_A3DC         | ROM     | 0000A3DC | 00000700 ~ |                                      |                    | c, ak v  | ersion misma | ccn exa- | +.4X 0  | CAA UXAA    | OXAA.  | , -(_DWC | orn .)(* | 00 - V2  | + 0X100 | 50010), | vz, v30,    | v29);  |

|                  |         |          | >          | 177                                  |                    |          |              |          |         |             |        |          |          |          |         |         |             |        |

| e 171 of 172     |         |          |            | • 178                                |                    |          | 0 * v2 + 0x1 | 0030018  | );      |             |        |          |          |          |         |         |             |        |

| Graph overview   |         |          | 0 # ×      | 179<br>188                           |                    | v30)     |              |          |         |             |        |          |          |          |         |         |             |        |

|                  |         | _        |            | • 181                                | sub_F478(          | 2, "GR s | ize mismatch | 0x%4.4)  | ( 0x00) | extex ext   | жx", * | _DWORD   | *)(20 *  | v2 + 0   | ×100300 | 10), v2 | , v37, v3   | e);    |

|                  |         |          |            | • 182                                |                    |          |              |          |         |             |        |          |          |          |         |         |             |        |

|                  |         |          |            | 183                                  |                    |          | * v2 + 0x10  | 100000   |         |             |        |          |          |          |         |         |             |        |

|                  |         |          |            | 189                                  |                    | ep -)(20 | - v2 + 0x10  | 0340628) | (v      | Do a OxPI   | ( ( ,  |          |          |          |         |         |             |        |

|                  |         |          |            | • 186                                |                    | >        |              |          |         |             |        |          |          |          |         |         |             |        |

|                  |         |          |            |                                      | 00010A60 sub_10710 |          | .00          |          |         |             |        |          |          |          |         |         |             |        |

Most strings were referenced immediately, ARM big endian was used here too.

It turned out that the newer chip (A5E30235063) was designed by Renesas.

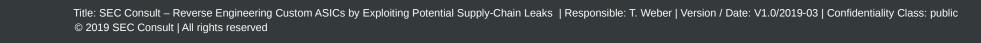

#### By brute forcing the 10-pin header of the PCB a JTAG port was found!

Connecting to target via JTAG TotalIRLen = 4. IRPrint = 0x01 JTAG chain detection found 1 devices: #0 Id: 0x4BA00477, IRLen: 04, CoreSight JTAG-DP Scanning AP map to find all available APs AP[3]: Stopped AP scan as end of AP map has been reached AP[0]: AHB-AP (IDR: 0x44770001) AP[1]: APB-AP (IDR: 0x24770002) AP[2]: JTAG-AP (IDR: 0x14760010) Iterating through AP map to find AHB-AP to use AP[0]: Skipped. Not an APB-AP AP[1]: APB-AP found ROMTbl[0][0]: CompAddr: 80008000 CID: B105900D, PID:04-003BB907 ETB ROMTbl[0][1]: CompAddr: 80003000 CID: B105900D, PID:04-003BB906 CTI ROMTbl[0][2]: CompAddr: 80004000 CID: B105900D, PID:04-001BB908 CSTF ROMTb}<del>[6][3]: CompAdd</del>r: 80002000 CID: B105900D, PID:04-007BBC14 Cortex-R4 Found Cortex-R4 r1p3 8 code breakpoints, 8 data breakpoints Debug architecture ARMv7.0 Data endian: big Main ID register: 0x411FC143 I-Cache L1: 16 KB, 128 Sets, 32 Bytes/Line, 4-Way D-Cache L1: 16 KB, 128 Sets, 32 Bytes/Line, 4-Way TCM Type register: 0x00010001 MPU Type register: 0x00000C00 System control register: Instruction endian: big Level-1 instruction cache disabled Level-1 data cache disabled MPU disabled Branch prediction enabled Memory zones: Default Default access mode AHB-AP (AP0) DMA like acc. in AP0 addr. space APB-AP (AP1) DMA like acc. in AP1 addr. space Cortex-R4 identified.

ARM Cortex R4 was identified. Now it was easy to trace the connections back to the chip!

**bláčk hat**

ASIA 2019

After removing the chip of an original S7 1211C, the traces can be followed back to the backside. JTAG can be enabled by adding an additional header to the PCB.

Beware, when you attach the debugger! It seems that Siemens have implemented a hardware module for deleting the flash memory when the CPU is stopped!!!

#### **Demo time!**

To provide a proof of concept, a small assembly program was written and uploaded to the PLC via the JTAG interface.

Special thanks goes to Dr. Ali Abbasi for providing me the UART MMIO address. https://www.syssec.ruhr-uni-bochum.de/chair/staff/aliabbasi/

Few days before publishing our research, we received the following statement from Siemens:

"The boards purchased by SEC Consult were not development boards but previously used or refurbished boards from Siemens devices. Siemens does not see a supply chain leak."

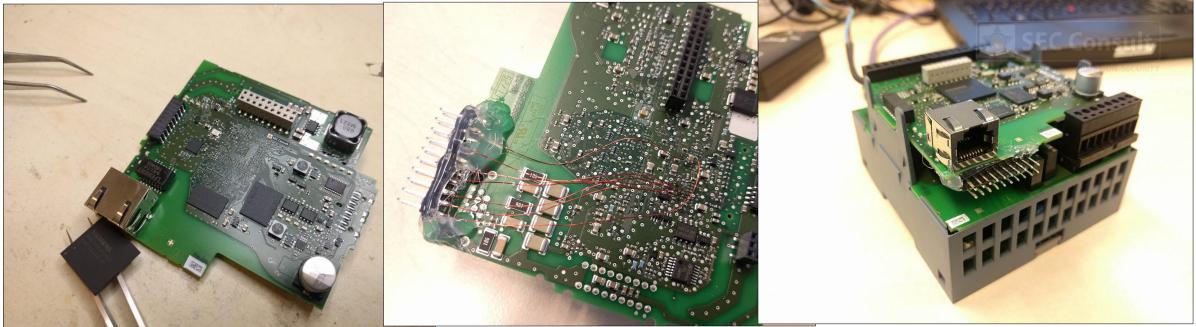

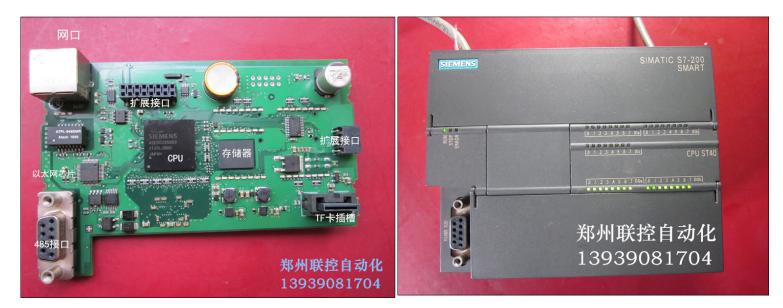

As it turns out, I was looking at boards from another series. The seller from Taobao fooled me. He offered boards from the older **S7-200 SMART** series labeled as **S7-1200** series ... but no bad feelings: the board had **JTAG**!

#### **Fun Fact**

#### Can you spot the similarities?

S7-200 SMART http://www.plcweixiu.com/news/html/390.html

#### One question on reddit, do you have another one?

| Siemens PLC JTAG Pinout Reverse Engineering (Reverse Engineering Architecture and Pinout of Cus<br>ASICS)                                                                                                                                   | tom |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| sec-consult.com/en/blo 🖸                                                                                                                                                                                                                    |     |

| 💭 2 Comments 🍌 Share 📱 Save                                                                                                                                                                                                                 |     |

| What are your thoughts? Log in or Sign up                                                                                                                                                                                                   | L   |

| SORT BY BEST -                                                                                                                                                                                                                              |     |

| 1/3/5/7/9/11/13/15 is pretty much default JTAG header and seems it matches the standards ,<br>Reply Share Report Save                                                                                                                       |     |

| Cool article. One thing I wished they explained was how they figured out which transistor to switch to ground. Was it from following the trace? Or some kind of intuitive knowledge that you get from experience<br>Reply Share Report Save |     |

## Thank you!

Find the full blogpost here:

https://sec-consult.com/en/blog/2019/02/reverse-engineering-architecture-pinout-plc/